# **Mixed Mode Simulation**

P. Fischer

Lehrstuhl für Schaltungstechnik und Simulation ZITI, Uni Heidelberg

(Based on slides from Florian Erdinger)

VLSI Design - Mixed Mode Simulation

© P. Fischer, ZITI, Uni Heidelberg Page 1

### Why Simulate in Mixed Mode?

- Most analog circuits need interaction with digital circuits

- control logic to steer the analogue part

- processing / verification of results

- Simple digital functionality can be obtained by spice sources (vpulse, vpwl,...), but this is tedious, inflexible,...

- (More flexibility by using Verilog-A. Good for simple extensions (DAC..), but not suited for large digital parts)

### $\rightarrow$ Mixed Mode Simulation:

- Digital parts:

- Hardware Description Language (Verilog, VHDL) very flexible

- Digital simulator

- Analog parts:

- Schematics

- Analog simulator

### Mixed Mode Simulation

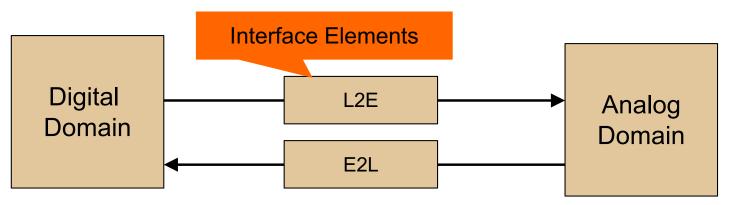

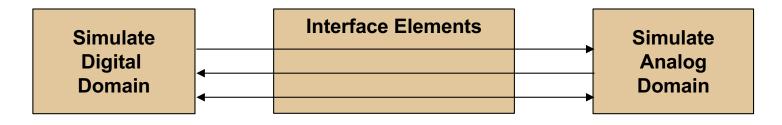

- Two simulators run in parallel

- Digital Sim. for digital part, Analogue sim. for analogue part

- Interface Elements translate between domains (what is 'True'?)

- Time must be (internally) synchronized between the sim.

- Advantages:

- Complex steering / logic easy to implement

- **Much** faster simulation in large designs (once it runs...)

- Drawbacks:

- More complex.

- Long simulator startup.

- There are many ways to do a Mixed Mode Simulation.

- I show here just one solution, which is easy to use for a start, but not so well suited for larger designs

- For large designs, it is efficient to

- first produce all 'netlists'

- work 'on the shell' to put things together and set up and run the simulation

These slides

• Extract results with a graphical viewer of automatically

Jargon: 'Digital on Top' vs. 'Analog on Top'

### What do we Need?

# A SIMPLE EXAMPLE

## Workflow

- The following slides show how to set up a simple Mixed Mode Simulation in the Virtuoso ADE environment. Steps:

- 1. Creating a *Verilog module* for stimulus with a matching *symbol*

- 2. Creating a *top-level simulation schematic* instantiating the Verilog symbol and some analog circuit connected to it

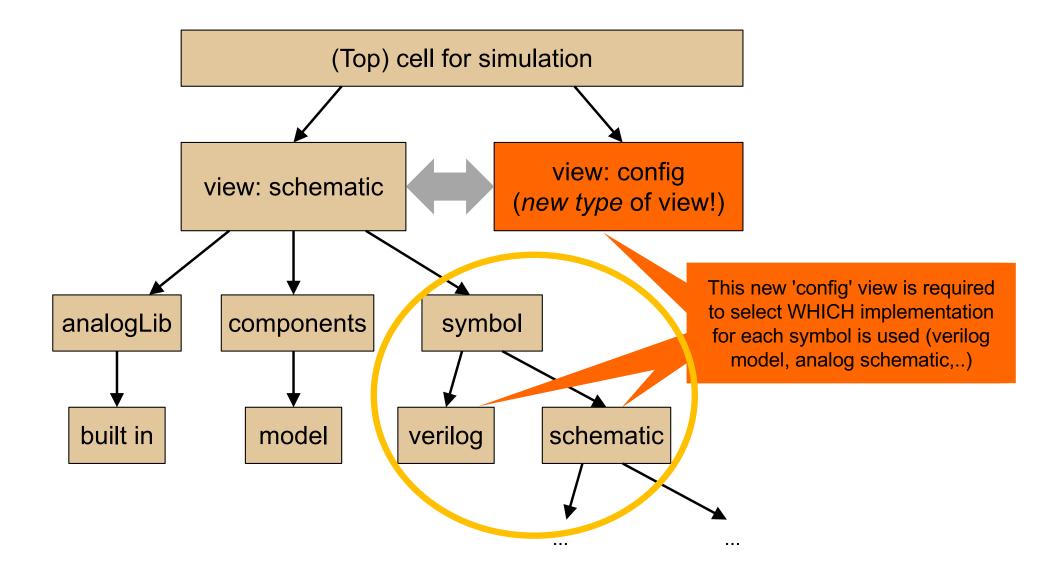

- 3. Creating a 'config' view of the top-level simulation schematic

- 4. Edit the config view telling the simulation what to do

- 5. Simulate using the AMS simulator

Note: The interface elements are created more or less automatically...

- We need to make the 'connectlib' available.

- Check your cds.lib or see in the library manager

Make sure you have the line SOFTINCLUDE \$IUSDIR/tools/inca/files/cds.lib

If this does not work, add it explicitly by adding SOFTINCLUDE /net/eda/INCISIV102/tools.lnx86/affirma\_ams/ etc/connect\_lib/cds.lib

### 1a. Creating a New Verilog Module

| File                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rife                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Library                                  | VLSI2324                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Cell                                     | VLSI2425_Stimulus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| View                                     | functional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Туре                                     | Verilog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Application                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Open with                                | Text Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| -                                        | his application for this type of file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Aiways use t                             | his application for this type of hie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Library path file                        | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| /home/fische                             | r/cadence/umc_018/0A/cds.lib                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | OK Cancel Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Text Edi                                 | tor (Verilog) Ve A _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| _                                        | tor (Verilog) Ve 🔺 💷 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Launch File                              | tor (Verilog) Ve × _ □ ×<br>Edit View Create » cādence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Launch File                              | tor (Verilog) Ve 🔺 💷 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Launch File                              | tor (Verilog) Ve A _ D X<br>Edit View Create » cādence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Launch File L<br>C - » Ba<br>1 //Verilog | tor (Verilog) Ve ∧ _ □ ×<br>Edit View Create »cādence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Launch File I                            | tor (Verilog) Ve A _ O X<br>Edit View Create » cādence<br>Control Control |

| Launch File I                            | tor (Verilog) Ve A _ O X<br>Edit View Create > cadence<br>Sic > > 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Launch File I                            | tor (Verilog) Ve A _ O X<br>Edit View Create > cadence<br>Sic > > 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Launch File I                            | tor (Verilog) Ve A _ O X<br>Edit View Create > cadence<br>Sic > > 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Launch File I                            | tor (Verilog) Ve A _ O X<br>Edit View Create > cadence<br>Sic > > 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Launch File I                            | tor (Verilog) Ve A _ O X<br>Edit View Create > cadence<br>Sic > > 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Launch File I                            | tor (Verilog) Ve A _ O X<br>Edit View Create > cadence<br>Sic > > 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Launch File I                            | tor (Verilog) Ve A _ O X<br>Edit View Create > cadence<br>Sic > > 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

- We will use this module to generate a rectangular signal to stimulate our analogue circuit.

- In 'Library Manager:

- File  $\rightarrow$  New  $\rightarrow$  Cell View

- 'Cell': name of verilog module

- 'Type': Verilog

- 'View': will change to 'functional'

- The Cadence text editor opens with an empty Verilog module

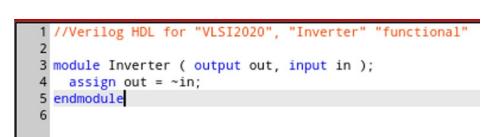

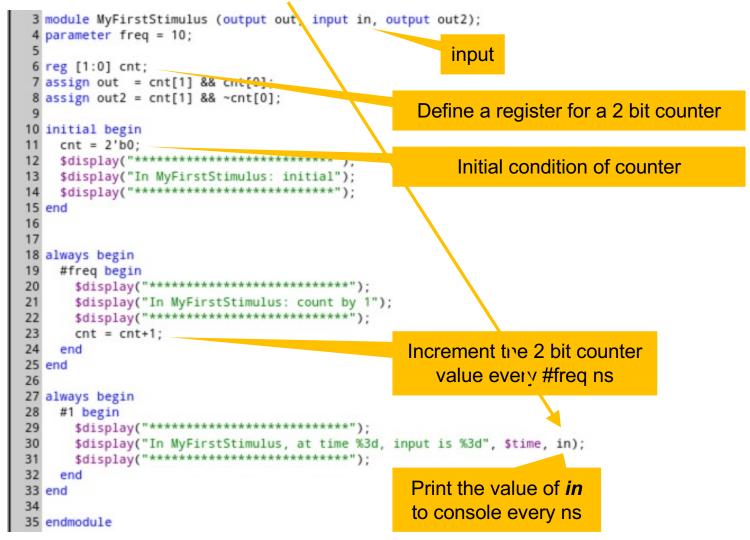

## 1b. Fill the Verilog Module

- Fill the Verilog module with some code.

- The code does *not* have to be synthesizable

- You may use parameters.

- For instance

(1 time step = 1 ns by default)

- When you close the text file, it is automatically parsed. This takes a moment.

- Correct it until there are no errors left.

- In my editor, the log file can be seen with View->Parser Log

- Error messages of Verilog compilation end up in .cadence/dfII/TextSupport/Logs/Parser/verilog...

- Use the latest file there

### 1c. Create the Symbol

- When the Verilog file is closed, the tool offers to create a symbol if there is none (or to modify an existing symbol which does not fit to the declared interface).

- Create the symbol.

- You may then edit the symbol to make it nicer.

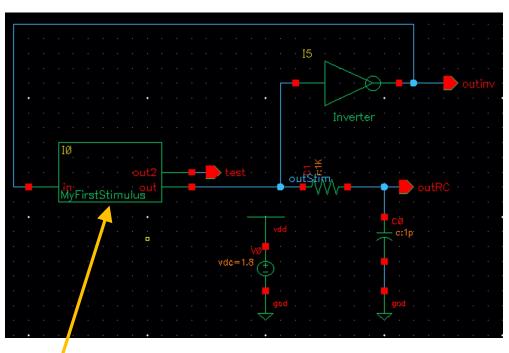

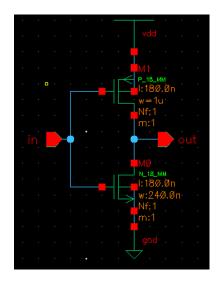

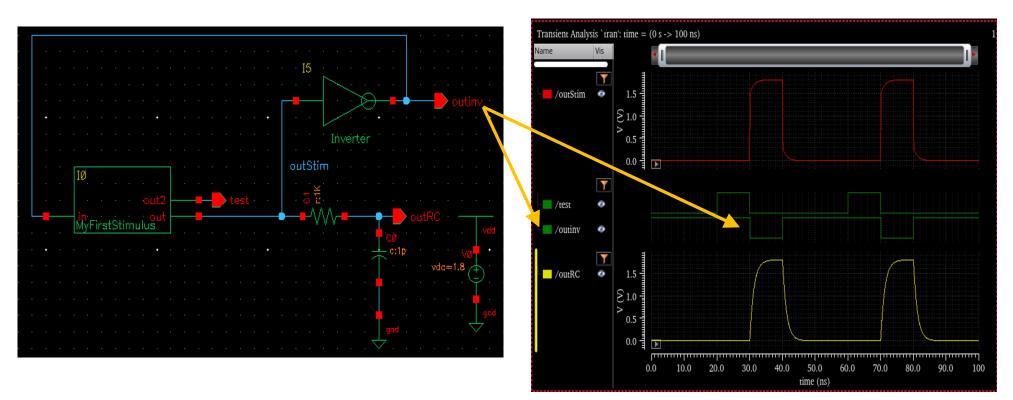

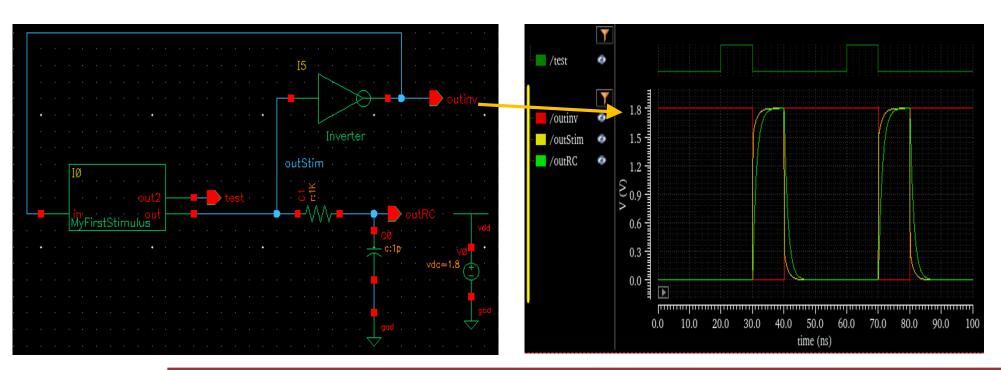

## 2. Creating A Top-Level Simulation Module

- In 'Library Manager'

- File  $\rightarrow$  New  $\rightarrow$  Cell View

- Create a schematic

- Put an instance of your Verilog module, i.e. the symbol

- If the Verilog contains *parameters*, the symbol inherits them.

- To see them: In the instantiated symbol, select CDF Parameter of view -> functional (not 'Use Tool Filter')

- Add some analog circuit (symbols, primitives, sources, ...) which can also be in symbols.

## 3. Creating the Simulation Configuration View

|              | New File             | •             | Ф 🗆 8         | ×            |      |         |      |

|--------------|----------------------|---------------|---------------|--------------|------|---------|------|

| File         |                      |               |               |              |      |         |      |

| Library      | VLSI2020             |               |               |              |      |         |      |

| Cell         | MixedSi              | m2            |               |              |      |         |      |

| View         | config               |               |               |              |      |         |      |

| Туре         | config               |               | 3             |              |      |         |      |

| Application  |                      | _             |               |              |      |         |      |

| Open with    | Hierarchy            | Editor 🔽      |               |              |      |         |      |

| Always us    | se this application  | for this type | of file       |              |      |         |      |

| Library path | file                 |               |               |              |      |         |      |

| $\odot$      |                      | New Confi     | guration      |              | 2    | $\odot$ | Ģ    |

|              | 1ixedSim<br>chematic |               |               |              |      | -       |      |

| Global Bir   |                      |               | Use Template  |              | 0 0  |         |      |

| Library Li:  | r 🔾 🛇                |               | ose rempiace  |              | 00   | 0       |      |

| View List:   | Name: AM             | ИS            |               |              |      |         |      |

| Stop List:   | From File: 7h        | ome/fischer/  | hierEditor/te | mplates      | /AMS |         |      |

| Constraint   |                      |               |               |              |      |         |      |

| Descriptic   | •                    | OK Ca         | ncel Ap       | ply)         | Help |         |      |

|              |                      |               |               |              |      |         |      |

|              |                      |               |               |              |      | $\succ$ |      |

|              |                      |               |               |              |      |         |      |

|              |                      |               |               |              |      |         | - J. |

|              |                      |               |               |              |      |         |      |

|              | -                    |               |               | $\checkmark$ |      |         |      |

- The AMS simulator needs a 'config' view for the simulation schematic

- In 'Library Manager:

- Select your simulation schematic

- File  $\rightarrow$  New  $\rightarrow$  Cell View

- 'Type': config (name changes to 'config')

- Note that 'Application' switches automatically to 'Hierarchy Editor'

- In the next window: change 'View' to 'schematic'

- Click 'Use Template' (bottom)

- Select 'AMS' (this will be our simulator)

• OK

OK

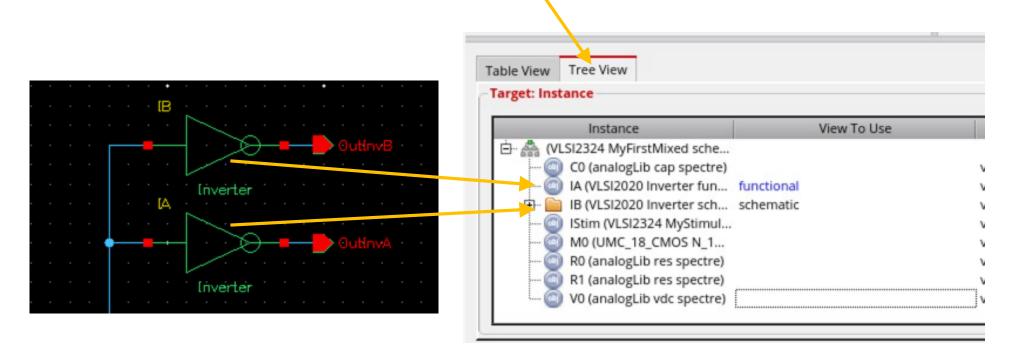

# 4. Changing 'config' view with the Hierarchy Editor

- The config view is edited in the 'Hierarchy Editor' and configures the netlisting procedure for simulation.

- Cells can have multiple representations, for instance a 'verilog' view and a 'schematic' view at the same time.

- The config view specifies the view to use for netlisting for each cell (or even instance)

|                                          | Launch <u>File Edit View</u>                            | oso® Hierarchy Edito | or: New Configura | tion (Save Needed        | l) (+ = ×<br>cādence     | A cell can have                                                               |     |

|------------------------------------------|---------------------------------------------------------|----------------------|-------------------|--------------------------|--------------------------|-------------------------------------------------------------------------------|-----|

|                                          | Top Cell                                                | ) 🥱 🥐 🕕 🖶 🦂          | Search            | Global Bindings          | Update Needed            | several view, e<br>'verilog',                                                 | .g. |

| 'Table view'<br>lists cells per<br>type. | Library: VLSI2020<br>Cell: MixedSim2<br>View: schematic | AD                   |                   | Library List: basic anal | ogLib                    | 'functional' or<br>'schematic'.<br>The view to use<br>is specified <b>her</b> | -   |

| 'Tree view'<br>shows all                 | Table View Tree View                                    |                      |                   |                          |                          |                                                                               |     |

| instances                                | Library                                                 | Cell                 | View Found        | View To Use              | Inherited View List      |                                                                               |     |